PLA (C64-Chip)

Die PLA ist ein Chip des C64, der die Ansteuerung des RAMs und weiterer Bausteine übernimmt. Die im C16 oder Plus/4 eingesetzten PLA-Chips sind zu C64-Boards nicht kompatibel. Dieser Artikel behandelt nur die PLA im C64.

Allgemeines[Bearbeiten | Quelltext bearbeiten]

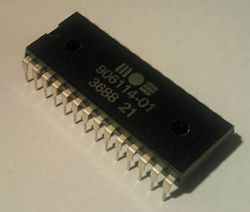

Die PLA (Abkürzung für Programmable Logic Array) ist ein (einmalig) hardwareprogrammierbarer Logik-Chip. Sie ist beim C64 bereits fertig programmiert verbaut (mit der Bezeichnung 906114-01 bzw. 251064-01; der generische unprogrammierte Chip trägt die Bezeichnung 82S100) und stellte für Commodore einen kostengünstigen Ersatz für eine größere Anzahl von Logik-ICs dar, die ansonsten nötig gewesen wären.

Die PLA steuert die Enable-Leitungen fast aller anderen Bausteine im C64 an: Sie entscheidet, welcher Chip beim Zugriff auf welche Adresse letztendlich angesprochen wird, was neben der Adresse an sich von zahlreichen anderen Faktoren (u.a. Zustand des Prozessorports, Taktzyklus-Phase, gewählte VIC-II-Bank) abhängt.

Die PLA setzt insbesondere das sogenannte Bankswitching beim C64 um, über das die CPU auf die 64 KByte RAM, 20 KByte ROM, 512 Byte Farbram, die Register diverser Chips (CIA, SID, VIC) und ggf. weitere über den Expansionsport angeschlossene Hardware zugreifen kann, obwohl die CPU eigentlich nur 64K Adressen insgesamt ansprechen kann.

Von BASIC aus lässt sich an der Speicherbelegung bzw. der Sicht der CPU auf den Speicher allerdings nicht viel ändern, da das Betriebssystem des C64 fest von seiner Standard-Speicherkonfiguration ausgeht und abstürzt, wenn sie geändert wird.

Auf der Hauptplatine mit der ASSY 250469 wurde ein 64poliger Multifunktions-Chip (251715-01 ohne bzw. 252535-01 mit integriertem Farb-RAM) verbaut, der neben der PLA auch weitere ICs integriert.

Anschlüsse der PLA[Bearbeiten | Quelltext bearbeiten]

Ein- und Ausgänge[Bearbeiten | Quelltext bearbeiten]

Die PLA hat 16 Eingangsleitungen:

- Von der CPU: LORAM, HIRAM, CHAREN aus dem Prozessorport ($01), A12-A15 vom Adressbus, R/W

- Vom VIC: VA12, VA13 vom Adressbus, CAS, AEC, BA

- Von der CIA2: VA14

- Vom Expansionsport: GAME, EXROM

und 8 Ausgangsleitungen:

- Zum RAM: CASRAM

- Zu den ROMs: BASIC, KERNAL, CHAROM (zu den jeweiligen Enable-Pins)

- Zum Farbram: GR/W

- Zum SID, VIC und Farbram: I/O (steuert über Demultiplexer U15 die Enable-Pins der jeweiligen Chips an)

- Zum Expansionsport: ROML, ROMH

Zum grundsätzlichen Verständnis des C64-Speichermodells relevant sind dabei nur LORAM, HIRAM, CHAREN, die ROM-Leitungen und I/O.

Die genaue Beschaltung ist unter Hardware-Aufbau des C64 beschrieben.

Steckmodule[Bearbeiten | Quelltext bearbeiten]

Steckmodule am Expansionsport können über die Leitungen GAME und EXROM die Speicheraufteilung des C64 beeinflussen. Auf den Modulen vorhandene ROMs können direkt durch ROML und ROMH angesteuert werden.

Pinbelegung[Bearbeiten | Quelltext bearbeiten]

Funktion[Bearbeiten | Quelltext bearbeiten]

Die PLA legt fest, an welchen Adressen für die CPU des C64 welche Daten sichtbar sind. Dabei sind in den ersten vier KByte des C64-Adressraums immer RAM sichtbar. Ausnahme dabei sind die Speicherstellen $0000 und $0001, in denen immer Datenrichtungsregister und Prozessorport der CPU eingeblendet sind. Was in den restlichen Zonen sichtbar ist, hängt von den Einstellungen LORAM, HIRAM, CHAREN aus dem Prozessorport ($01) der CPU ab. Ferner können Steckmodule über die Leitungen GAME und EXROM Einfluss nehmen.

Weitere Erklärungen zur Belegung der einzelnen Bereiche finden sich unter Speicherbelegungsplan.

| # | Leitungen | Adressraum | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Steckmodul | Prozessorport | 4096–32767 $1000–$7FFF |

32768–40959 $8000–$9FFF |

40960–49151 $A000–$BFFF |

49152–53247 $C000–$CFFF |

53248–57343 $D000–$DFFF |

57344–65535 $E000–$FFFF | ||||

| GAME | EXROM | CHAREN Bit 2 | HIRAM Bit 1 | LORAM Bit 0 | |||||||

| 1 | 1 | 1 | 1 | 1 | 1 | Int. RAM | Int. RAM | BASIC ROM | Int. RAM | I/O | Kernal ROM |

| 2 | 1 | X | 1 | 1 | 0 | Int. RAM | Int. RAM | Int. RAM | Int. RAM | I/O | Kernal ROM |

| 3 | 1 | X | 1 | 0 | 1 | Int. RAM | Int. RAM | Int. RAM | Int. RAM | I/O | Int. RAM |

| 4 | 1 | X | X | 0 | 0 | Int. RAM | Int. RAM | Int. RAM | Int. RAM | Int. RAM | Int. RAM |

| 5 | 1 | 1 | 0 | 1 | 1 | Int. RAM | Int. RAM | BASIC ROM | Int. RAM | Charset ROM | Kernal ROM |

| 6 | 1 | X | 0 | 1 | 0 | Int. RAM | Int. RAM | Int. RAM | Int. RAM | Charset ROM | Kernal ROM |

| 7 | 1 | X | 0 | 0 | 1 | Int. RAM | Int. RAM | Int. RAM | Int. RAM | Charset ROM | Int. RAM |

| 8 | 1 | 0 | 1 | 1 | 1 | Int. RAM | Cart. Low | BASIC ROM | Int. RAM | I/O | Kernal ROM |

| 9 | 1 | 0 | 0 | 1 | 1 | Int. RAM | Cart. Low | BASIC ROM | Int. RAM | Charset ROM | Kernal ROM |

| 10 | 0 | 1 | X | X | X | Offen | Cart. Low | Offen | Offen | I/O | Cart. High |

| 11 | 0 | 0 | 1 | 1 | 1 | Int. RAM | Cart. Low | Cart. High | Int. RAM | I/O | Kernal ROM |

| 12 | 0 | 0 | 1 | 1 | 0 | Int. RAM | Int. RAM | Cart. High | Int. RAM | I/O | Kernal ROM |

| 13 | 0 | 0 | 1 | 0 | 1 | Int. RAM | Int. RAM | Int. RAM | Int. RAM | I/O | Int. RAM |

| 14 | 0 | 0 | X | 0 | 0 | Int. RAM | Int. RAM | Int. RAM | Int. RAM | Int. RAM | Int. RAM |

| 15 | 0 | 0 | 0 | 1 | 1 | Int. RAM | Cart. Low | Cart. High | Int. RAM | Charset ROM | Kernal ROM |

| 16 | 0 | 0 | 0 | 1 | 0 | Int. RAM | Int. RAM | Cart. High | Int. RAM | Charset ROM | Kernal ROM |

| 17 | 0 | 0 | 0 | 0 | 1 | Int. RAM | Int. RAM | Int. RAM | Int. RAM | Int. RAM | Int. RAM |

| X: Wert spielt keine Rolle | |||||||||||

Der Strich über den Bezeichnungen der Leitungen-Spalten bedeutet, dass die Leitungen eine invertierte Bedeutung haben, also vom Typ Active-Low sind. Die jeweilige Funktion wird dann aktiv, wenn das Signal mit logischem Signalpegel 0 anliegt.

Offen in Konfiguration 10 bedeutet, dass kein Speicherbaustein oder Register eines IO-Chips angesprochen wird bzw. im Adressraum eingeblendet ist und somit der Adressraum quasi in der Luft hängt. Lesezugriffe liefern keinen definierten Wert.

Alternative Darstellungen:

- PLA-Signalmatrix und Erklärung (engl.) aus The Transactor Volume 6, Issue 05, S. 51ff.

Ultimax-Modus[Bearbeiten | Quelltext bearbeiten]

Der Kompatibilitätsmodus für Ultimax-Steckmodule (Konfiguration 10) ist eine Besonderheit. Da die Max Machine/Ultimax keine eigenen ROMs (BASIC/KERNAL/CHARROM) hatte, wird in diesem Modus das ROM des Moduls als "KERNAL" und auch als CHARROM benutzt. In C64-Modulen wird dieser Modus häufig zur Implementierung von Freezern benutzt, da per eigenen ROM bei $Exxx/$Fxxx der NMI-Vektor überschrieben werden kann. Außerdem sind etliche Speicherbereiche in diesem Modus "offen", es können vom Modul also im Steckmodul befindliche Bausteine in diesen Bereichen eingeblendet werden.

Eine weitere Besonderheit des Ultimax-Modus ist, dass der VIC-II (der in allen anderen Konfigurationen in den 4k-Blöcken ab $1000 und $9000 das Zeichensatz-ROM und ansonsten das C64-RAM sieht) hier bei $3xxx/$7xxx/$Bxxx/$Fxxx das Hi-ROM des Cartridges und ansonsten das C64-interne RAM sieht (Details siehe Hardware-Aufbau des C64). Dies ist also der einzige Modus, in dem dem VIC von einem Cartridge direkt Daten "zugespielt" werden können - leider nur jeweils 4k, also nicht genug für (Vollbild-)Grafik direkt per Modul.

Im Ultimax-Modus werden auch bei Schreibzugriffen auf die ROM-Bereiche die jeweiligen ROMs aktiviert, während andere Modi bei Schreibzugriffen stattdessen das RAM aktivieren.

Timings[Bearbeiten | Quelltext bearbeiten]

Der Ausgang CASRAM aktiviert die RAMs; das darf erst eine kurze Zeit nach dem Wechsel des Eingangs CAS passieren, da CAS auch via U13/U25 die hohen 8 Bits des Adressbusses an die RAMs anlegt (Details siehe hier). CASRAM darf erst aktiv werden, wenn diese Adressen an den RAMs stabil anliegen, was ein paar dutzend Nanosekunden dauert. Diverse Versionen der PLA (und auch des VIC-II) haben hier unterschiedliche Timings, weswegen auf der Hauptplatine des C64 (ab der ASSY 250407) RC-Glieder zum Einstellen der Verzögerung vorgesehen wurden (siehe nächster Abschnitt).

Beim Ausgang GR/W handelt es sich um das verzögerte R/W des Prozessors, da das Color-SRAM erst die Schreibaufforderung bekommen darf, wenn die Adressen schon eine zeitlang anlagen (der 6510 setzt R/W jedoch beinahe zeitgleich mit den Adressen). Die PLA synchronisiert dazu das Signal u.a. mit CAS.

Manche Steckmodule verlassen sich darauf, dass die PLA sehr kurzzeitige Glitches auf den Adressleitungen ignoriert. Zum Beispiel kann es bei aktiviertem EXROM vorkommen, dass beim Wechsel des Adressbusses von $Fxxx im VIC-II-Halbzyklus auf $0xxx im CPU-Halbzyklus zwischenzeitlich $8xxx am Adressbus sichtbar ist und dadurch - bei einer schnellen PLA-Umsetzung - ROML kurzzeitig aktiviert würde, was z.B. das Super Zaxxon-Cartridge zum Absturz bringt.[1]

Versionen[Bearbeiten | Quelltext bearbeiten]

28 Pins[Bearbeiten | Quelltext bearbeiten]

906114-01 und 251064-01 sind von den Logiktermen her baugleich, aber das Timing ist nicht ganz dasselbe. Die 251064-01 wurde von Fujitsu hergestellt, im Schaltplan zur 250407 wird sie auch als 'MB112A101' bezeichnet. MB ist das Herstellerkennzeichen von Fujitsu. Auch das Gehäuse dieses Chips ist eindeutig Fujitsu, wie man an der Längskerbe erkennen kann, die zur Markierung von Pin 1 dient.

- Laut Schaltplan der Assy 250407 will die 251064-01 einen bestückten C204 mit 82pF haben. Das ist ein Kondensator zwischen GND und den CAS-Pins der RAMs (also nachdem CAS durch die PLA und R42 gelaufen ist).

- Die 906114-01 will hingegen einen C203 bestückt haben, 82 pF zwischen CAS am VIC-II und GND (also bevor CAS durch die PLA geht).

- Eine Ausnahme ist der VIC-II 6569R3, dann darf C203 nicht bestückt sein.

64 Pins[Bearbeiten | Quelltext bearbeiten]

Die Multifunktions-Chips der Assy 250469 benutzen statt der 28-Pin-PLA der früheren Versionen einen weiter integrierten Chip mit 64 Pins.

- Im Multifunktions-Chip 251715-01 sind die PLA sowie die früheren ICs U13/U25/U14/U16/U26/U15 integriert.

- Die Version 252535-01 des Multifunktions-Chips (genutzt auf der Assy 250469 Rev B) integriert zusätzlich das Farb-RAM (früher U19 bzw. U6).

______________________

| !____! |

01 --| A13 Vdd |-- 64

02 --| A14 A12 |-- 63

03 --| A15 A11 |-- 62

04 --| R/W A10 |-- 61

05 --| /LORAM A9 |-- 60

06 --| /HIRAM A8 |-- 59

07 --| /CHAREN A7 |-- 58

08 --| NMI A6 |-- 57

09 --| RESTORE A5 |-- 56

10 --| /VA14 A4 |-- 55

11 --| /VA15 A3 |-- 54

12 --| /CIA2 A2 |-- 53

13 --| /CHAROM A1 |-- 52

14 --| /BASIC A0 |-- 51

15 --| /KERNAL¹³ /ROMH |-- 50

16 --| GND /IO1 |-- 49

17 --| /COLRAM ³MODE |-- 48

18 --| CD0² /GAME |-- 47

19 --| CD1² /EXROM |-- 46

20 --| CD2² /IO2 |-- 45

21 --| CD3² /ROML |-- 44

22 --| /CASRAM /SID |-- 43

23 --| RAM R/W VA7 |-- 42

24 --| MA6 VA6 |-- 41

25 --| MA3 /VIC |-- 40

26 --| MA0 BA |-- 39

27 --| MA2 AEC |-- 38

28 --| MA4 Φ0 |-- 37

29 --| MA1 /RAS |-- 36

30 --| MA5 /CAS |-- 35

31 --| MA7 /CIA1 |-- 34

32 --| NC GND |-- 33

|______________________|

¹ Bei der 252535-01 Enable des kombinierten KERNAL/BASIC-ROMs

² Bei der 252535-01 Datenbits des Farb-RAM

³ Siehe Artikel Hauptplatine zu Details

Ersatz der PLA[Bearbeiten | Quelltext bearbeiten]

Die PLA ist einer der anfälligeren Bausteine im C64 und bekannt für häufige Defekte. Die höher integrierte PLA bei C64 Assy No. 250469 ist weniger anfällig, hält jedoch auch nicht ewig.

Einfacher Ersatz der normalen PLA ist mit einem EPROM und Anschlussadapter möglich, jedoch funktioniert das in längst nicht jedem Anwendungsfall und kann insbesondere im Zusammenspiel mit Steckmodulen Probleme machen.[2][3] Beim Zustandswechsel der Eingangsleitungen ergeben sich auf den Ausgangsleitungen eines EPROMs kurzzeitig undefinierte Zwischenzustände; bei PLDs ist das nicht der Fall. Besonders kritisch ist dabei das CASRAM-Signal für das RAM, bei dem "Signalschwinger" einen Speicherzugriffszyklus starten können. Angeschlossene Steckmodule oder Erweiterungen, wie bspw. KERNAL-Umschalt-Platinen, können diese Probleme verstärken.[4]

Über die Jahre wurden (und werden z.T. auch immer wieder) von verschiedener Stelle nicht-typisierte Ersatz-PLA vertrieben. Dabei handelte es sich meist um die erwähnten EPROM-"PLA", gebrannte PLD oder CPLD-Nachbauten.[5]

Dagegen existieren auch weitestgehend kompatible PLA-Ersatzschaltungen, die eigens entworfen und vertrieben wurden bzw. werden. Auch hier kann es unter verschiedenen Umständen aber durchaus mal zu Inkompatibilitäten kommen.

Bekannt sind vor allem folgende Entwicklungen:

- Die SuperPLA von Jens Schönfeld kann auch in einem C264-Rechner verwendet werden.

- Die realPLA von skoe.

- PLAnkton von e5frog.

- Die PLAdvanced+ kann auf zahlreichen verschiedenen Commodore-8-Bit-Rechnern eingesetzt werden.

- Die PLA20V8 von Daniël Mantione.

Der 64-polige Multifunktions-Chip auf 250269-Boards ist im Vergleich weniger defektanfällig.

Ein PLA-Kompatibilitätstest ist das EasyFlash3-CRT zu Fix-It Felix Jr.: Bevor das Spiel startet, läuft eine kleine Intro-Sequenz, in dem ein Bagger den Baumstumpf von Antagonist Ralph wegschiebt, worauf sich dieser bitter beschwert. Genau in dieser Sequenz gibt es massive Sprite-Fehler mit einer inkompatiblen PLA.

Ein weiterer Test ist das Steckmodul zu Super Zaxxon (nur das Original-Steckmodul, nicht dessen Emulation in z.B. Kung Fu Flash!); das Spiel stürzt bei Spielbeginn bei inkompatiblen PLAs ab (Details siehe Abschnitt "Timings").

Weblinks[Bearbeiten | Quelltext bearbeiten]

- "The C64 PLA Dissected" - Dokument zum PLA Reverse Engineering von Thomas Giesel (skoe)

- pla.txt

- PLA-Schaltungslogik für die alten 82S100-PLAs

- PLA-Schaltungslogik für die alten 82S100-PLAs - "Video PLA Austausch" "Troubleshooting a "back screen" C64"

PLA Chip-Fehler feststellen & beheben von Adrian Black

PLA Chip-Fehler feststellen & beheben von Adrian Black - PLA20V8 Seite des Entwicklers zum PLA-Ersatz auf GAL20V8-Basis

Quellen[Bearbeiten | Quelltext bearbeiten]

- ↑ Zu Signal-Glitches: Super Zaxxon Replica

und Thema: p64oPLA - C64-PLA-Ersatz und -Tester auf Basis des RP2040/2350 auf Forum64.de

und Thema: p64oPLA - C64-PLA-Ersatz und -Tester auf Basis des RP2040/2350 auf Forum64.de

- ↑ Thema: Neues aus EPROMhausen auf Forum64.de

- ↑ Thema: PLA > EPROM geht nicht mit EasyFlash auf Forum64.de

- ↑ 'The PLAin Truth About the Commodore 64 PLA' at World of Commodore 2017 auf YouTube (36:12)

zeigt Glitches bei EPROM-PLAs

zeigt Glitches bei EPROM-PLAs

- ↑ Thema: Ersatz-PLA macht Cevi instabil? auf Forum64.de

Hardware-Aufbau des C64 · Hardware-Portalseite

Komponenten des C64: CPU · VIC · SID · CIA · PLA · RAM · ROM · Farb-RAM