MOS 6510

|

Dieser Artikel ist sehr kurz und nicht besonders ausführlich. Hilf bitte mit, ihn zu verbessern. |

1983 - Kalenderwoche 50

Der MOS 6510-Mikroprozessor ist eine 8-Bit-CPU (damals auch häufiger "MPU" genannt), der von der Firma Commodore entwickelt wurde. Bekannt wurde der 6510 insbesondere, weil er die CPU des C64 war. Die interne Prozessorarchitektur ist fast identisch mit der des MOS 6502-Mikroprozessors - insbesondere ist der Befehlssatz aufwärtskompatibel. Das heißt, ein Programm, das für den 6502 geschrieben wurde, läuft ohne Änderung auch auf dem 6510. Die CPU ist also in Bezug auf Opcodes völlig 6502-kompatibel, selbst hinsichtlich aller Maskenfehler und illegaler Opcodes (siehe Opcode-Matrix).

Der 6510 im C64[Bearbeiten | Quelltext bearbeiten]

Der 6510 ist im C64 mit 985.248 Hz (PAL-Version) respektive 1.022.727 Hz (NTSC-Version) getaktet. Ein Taktzyklus dauert entsprechend etwa 0,000001 Sekunden, also etwa 1 µS (Mikrosekunde).

Unterschiede zum MOS 6502[Bearbeiten | Quelltext bearbeiten]

- Zusätzlicher 6-Bit-I/O-Port (Prozessorport).

- Der Adressbus und der Datenbus kann hochohmig geschaltet werden.

- Beim C64 ist das nötig, da der VIC-II zeitweise den Bus übernimmt, u.a. für das Refresh des dynamischen RAMs und für den Zugriff auf Grafikdaten für die Bildschirmdarstellung.

- Keine Leitung für das Overflow-Flag.

- Keine Leitung für das SYNC-Signal.

Varianten[Bearbeiten | Quelltext bearbeiten]

- 8500

- wurde auf dem C64-Board ASSY-250469 verwendet

- wurde offiziell ab 1987 verwendet

- 6510 und 8500 sind 1:1 austauschbar.

- 7501/8501

- 8502

- wurde im C128 eingesetzt

- besitzt eine 2 MHz Umschaltung

- besitzt 7 Ein-/Ausgabeleitungen

- 6510T

- besitzt 8 Ein-/Ausgabeleitungen

- wurde in der Floppy 1551 eingesetzt

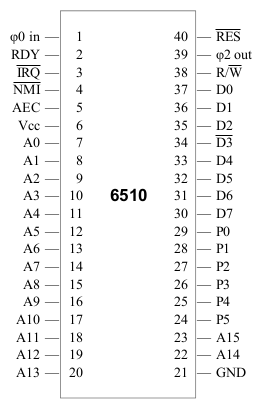

Pinbelegung des MOS 6510[Bearbeiten | Quelltext bearbeiten]

| Pin | Beschreibung | |

|---|---|---|

|

Φ0 (phi0) in | Systemtakt (Eingang) |

| RDY | Ready (Eingang) - bei LOW wartet die CPU nach dem nächsten Leseyklus bis die Leitung wieder auf HIGH geht | |

| IRQ | Interrupt-Request (Eingang), bei LOW wird Interrupt ausgelöst | |

| NMI | Interrupt-Request (Eingang), bei LOW-Flanke wird NMI ausgelöst | |

| AEC | Address Enable Control (Eingang) - bei LOW werden Adress- und Datenbus sowie R/W hochohmig geschaltet/entkoppelt | |

| Vcc | Versorgungsspannung +5V DC | |

| A0 - A15 | Adressleitungen (Ausgang) | |

| GND | Systemmasse | |

| P0 - P5 | I/O-Port/Prozessorport (Ein-/Ausgang) | |

| D0 - D7 | Datenbus (Ein-/Ausgang) | |

| R/W | Ausgang - bei HIGH wird vom Datenbus gelesen, bei LOW geschrieben | |

| Φ2 (phi2) out | Systemtakt (Ausgang) zur Synchronisation mit den restlichen Systemkomponenten | |

| RES | Reset (Eingang) - bei LOW wird ein Reset ausgelöst |

Weblinks[Bearbeiten | Quelltext bearbeiten]

| Wikipedia: MOS Technology 6510 |

- MOS 6510

Technisches Datenblatt

Technisches Datenblatt - Documentation for the NMOS 65xx/85xx Instruction Set

- sehr ausführliche technische Informationen

- sehr ausführliche technische Informationen - MCL64, ein Microcontroller-basierter Ersatz für einen 6510

Hardware-Aufbau des C64 · Hardware-Portalseite

Komponenten des C64: CPU · VIC · SID · CIA · PLA · RAM · ROM · Farb-RAM