VIC

Die Bezeichnung bzw. Abkürzung VIC steht bei Commodore-Heimcomputern für Video-Interface-Chip, der für die Erzeugung der Grafikausgabe zuständig ist (Zeichen, Bitmapgrafik).

Die Chips wurden vom Halbleiterhersteller MOS Technology produziert, den Commodore 1976 übernommen hatte.

Der im VC20 für Ton- und Grafikausgabe verwendete VIC 6560/6561 wird als "Original" VIC-Chip bezeichnet (1980, ca. 2000-3000 Transistoren[1]).

Der wesentlich veränderte Nachfolger VIC-II im C64, VC10 und der CBM500-Serie unterstützt u.a. zusätzlich Sprites (1982, ca. 9000-13000 Transistoren[2], 5µm-Prozess[3]) und ist mit Abstand der komplexeste Chip im C64.[4]

Der C128 benutzt eine leicht Veränderte Variante des VIC-II, den VIC-IIe.

VIC-Varianten[Bearbeiten | Quelltext bearbeiten]

Folgende Varianten des VIC-II wurden verwendet:

- Im C64 und seinen Varianten wie SX64, PET 64 oder C64 Games System: 6567, 8562 (NTSC) / 6569, 8565 (PAL)

- Entwickelt bis Ende 1981 von Albert Charpentier und Charles Winterble, präsentiert auf der Consumer Electronics Show Anfang 1982.

- Der 6569R1 besitzt ledliglich 5 Helligkeitsstufen, alle Revisionen danach können 9 Helligkeitsstufen darstellen.

- Achtung: An Pin 13/Vdd erwarten die NMOS-Chips 6566/67/69 +12V, die HMOS-II-Varianten (8562/65) erwarten +5V DC, sind also nicht ohne Weiteres gegeneinander tauschbar.

- Die 856x haben das sogenannte Grey Dots-Problem. Besonders betroffen oder bekannt ist das Problem bei den Varianten[5][6]

- PAL 8565R2-4191

- PAL 8565R2-3991(22)

- PAL 8565R2-0787(22)

- In der MAX Machine: 6566 (NTSC)

- In der CBM500-Serie: 6567 (NTSC) / 6569 (PAL)

Vorgänger und Nachfolger:

- Im VC20: VIC(-I) 6560 (NTSC) / 6561 (PAL)

- Im C128/D/DCR: VIC-IIe 8564 (NTSC), 8566 (PAL-B), 8569 (PAL-N)[7]

- Im C65: VIC-III 4567 "Bill"

Anbindung des VIC-II im C64[Bearbeiten | Quelltext bearbeiten]

Der VIC-II im C64 übernimmt einige Aufgaben, die man nicht in einem Grafikchip vermutet, so kümmert er sich z.B. um das Refresh des RAMs.

Der VIC-II kann die CPU, mit der er normalerweise im Wechseltakt auf den Speicher zugreift, zeitweise komplett anhalten. Außerdem ist das Farbram ist mit einen (zusätzlichen) eigenen Datenbus mit dem VIC-II verbunden.

Speicherbandbreite[Bearbeiten | Quelltext bearbeiten]

Der abwechselnde Zugriff auf das RAM mit der CPU und der eigene Bus zum Farbram ist nötig, da ansonsten die Speicherbandbreite für die Grafikfähigkeiten des VIC-II nicht ausreichen würde:

- Pro Bildschirmzeile müssen im Textmodus bei aktivierten Sprites 40 RAM-Zugriffe für Zeicheninformationen + 40 Zugriffe für Zeichen-Bitmapdaten + 40 Zugriffe[8] für Farbinformationen + 8 Zugriffe für Sprite-Pointer + 8x3 Zugriffe Sprite-Daten = 152 Zugriffe auf Daten ausgeführt werden.

- Dem VIC-II stehen aber nur 63 Takte minus 5 Takte für RAM-Refresh = 58 Bytes Speicherbandbreite pro Bildschirmzeile zur Verfügung.

Um dieses Problem zu lösen, wurden folgende Tricks beim Design des VIC-II umgesetzt:

- die Zeicheninformationen holt sich der VIC-II in Badlines und speichert sie in einem internen 40 Bytes großen Zwischenspeicher

- die Farbinformationen kommen aus dem separaten mit eigenem Datenbus (aber dem normalen Adressbus bzw. den unteren 10 Bits davon) angebundenen Farb-RAM

- zum Holen der Sprite-Daten wird die CPU angehalten, die Daten werden VIC-II-intern in acht 24-bittige Schieberegister zwischengespeichert

- nur die Zeichen-Bitmapdaten und Sprite-Pointer werden tatsächlich "live" aus dem RAM des Computers geholt, während die CPU weiterläuft.

Andere Möglichkeiten, die Bandbreite zu erhöhen, waren nicht möglich:

- ein komplettes VIC-II-eigenes separates Video-RAM wäre teuer gewesen und hätte zur Anbindung rund 20 zusätzliche Pins am Video-Chip gebraucht, was damals technisch nicht möglich war; z.B. der separate Videospeicher des VDC wurde dort durch eingeschränkte/langsame Anbindung des Chips zur CPU erkauft (nur ein einziges Adressbit). Bereits das Color-RAM des VIC-II konnte nur ohne eigenen Adressbus realisiert werden, und selbst der Reset-Pin wurde beim VIC-II eingespart.

- ein ähnlich großer On-Chip-Videospeicher war technisch nicht möglich.

- zwar erlaubt das RAM des C64 einen höheren Takt, aber die meisten für den C64 zur Verfügung stehenden Chips waren auf 1 MHz ausgelegt; die Nutzung der niedrigen Taktflanke exklusiv für den VIC-II war bereits ein Kniff; für den VIC-II war nur ein veralteter (aber günstiger) Herstellungsprozess vorgesehen, der höhere Taktraten vermutlich nicht geschafft hätte; und letztendlich war die Entwicklungszeit des C64 mit rund zwei Monaten viel zu begrenzt für weitere Tricks.

Details dazu finden sich im Artikel Hardware-Aufbau des C64.

Speicheradressen des VIC-II[Bearbeiten | Quelltext bearbeiten]

- Der VIC-II greift ausschließlich auf das RAM bzw. das Character-ROM zu. Die Konfiguration der PLA ist für den VIC - außer im Ultimax-Modus - nicht relevant. Das Character-ROM ist für den VIC an $1000 bzw. $9000 (Offset $1000 in Bank 0 bzw. Bank 2) sichtbar, siehe VIC-Bank.

- Sprites liegen bei Adresse MEM (Bildschirmspeicher + $03F8 + Sprite-Nummer)*64.

- Die Adresse des Bildschirmspeichers wird durch die gewählte VIC-Bank ($DD00, siehe CIA 2) und $D018 festgelegt.

- $D02F (beim VIC-II) bis $D03F werden nicht vom VIC-II dekodiert. Die CPU liest dort $FF. Geschriebene Werte werden ignoriert.

- Die VIC-Register erscheinen im CPU-Adressraum alle $40/64 Bytes von $D000 bis $D3FF. Z.B. $D060 ist also mit $D020 identisch.

| Adresse (hex) | Adresse (dez) | Register | Inhalt |

| $D000 | 53248 | 0 | X-Koordinate für Sprite 0 (0..255) |

| $D001 | 53249 | 1 | Y-Koordinate für Sprite 0 (0..255) |

| $D002 | 53250 | 2 | X-Koordinate für Sprite 1 (0..255) |

| $D003 | 53251 | 3 | Y-Koordinate für Sprite 1 (0..255) |

| $D004 | 53252 | 4 | X-Koordinate für Sprite 2 (0..255) |

| $D005 | 53253 | 5 | Y-Koordinate für Sprite 2 (0..255) |

| $D006 | 53254 | 6 | X-Koordinate für Sprite 3 (0..255) |

| $D007 | 53255 | 7 | Y-Koordinate für Sprite 3 (0..255) |

| $D008 | 53256 | 8 | X-Koordinate für Sprite 4 (0..255) |

| $D009 | 53257 | 9 | Y-Koordinate für Sprite 4 (0..255) |

| $D00A | 53258 | 10 | X-Koordinate für Sprite 5 (0..255) |

| $D00B | 53259 | 11 | Y-Koordinate für Sprite 5 (0..255) |

| $D00C | 53260 | 12 | X-Koordinate für Sprite 6 (0..255) |

| $D00D | 53261 | 13 | Y-Koordinate für Sprite 6 (0..255) |

| $D00E | 53262 | 14 | X-Koordinate für Sprite 7 (0..255) |

| $D00F | 53263 | 15 | Y-Koordinate für Sprite 7 (0..255) |

| $D010 | 53264 | 16 | Bit 8 für die obigen X-Koordinaten (Bitmaske: 0..255), jedes Bit steht für eines der Sprites von 0 bis 7. |

| $D011 | 53265 | 17 | Bit 7: Bit 8 von RASTER (siehe auch $D012). Lesen: MSB der aktuellen Rasterzeile. Schreiben: MSB der Rasterzeile, in der IRQ ausgelöst wird. Bit 6: Extended-Color-Modus (ECM, 1=an) Bit 5: Bitmap-Modus (BMM, 1=an) Bit 4: Bildausgabe an/aus (BLNK, 1=an, Effekt erst beim nächsten Einzelbild) Bit 3: 25/24 Zeilen (RSEL, 1=25 Zeilen) Bit 2..0: Offset Text/Grafik in Rasterzeilen vom oberen Bildschirmrand (YSCROLL), gilt nicht für Sprites Standard (BASIC-Prompt): $1b/27/00011011 |

| $D012 | 53266 | 18 | Bits 7..0 des RASTER-Registers. Bit 8 siehe $D011. Lesen: Aktuelle Rasterzeile Schreiben: Rasterzeile, bei der ein IRQ ausgelöst wird ($D011 beachten!) |

| $D013 | 53267 | 19 | Lightpen X-Koordinate (assoziiert mit Pin LP am VIC-Chip, halbe Auflösung im Vergleich zu anderen Registern in X-Richtung) |

| $D014 | 53268 | 20 | Lightpen Y-Koordinate |

| $D015 | 53269 | 21 | Sprite-Schalter, Bit = 1: Sprite n an (Bitmaske: 0..255) |

| $D016 | 53270 | 22 | Bit 7..5: unbenutzt Bit 4: Multicolor-Modus (MCM, 1=an) Bit 3: 40/38 Spalten (CSEL, 1=40 Spalten) Bit 2..0: Offset Text/Grafik in Pixeln vom linken Bildschirmrand (XSCROLL), gilt nicht für Sprites Standard (BASIC-Prompt): $c8/200/11001000 |

| $D017 | 53271 | 23 | Sprite-Schalter, Bit = 1: Sprite n doppelt hoch (Bitmaske: 0..255) |

| $D018 | 53272 | 24 | VIC-Speicherkontrollregister

Im Textmodus:

Z.B. bei Bit 3…0 = 0101 erwartet der VIC den Zeichensatz bei Adresse 4096/$1000 innerhalb der gewählten VIC-Bank.

Z.B. bei Bit 3…0 = 1000 erwartet der VIC die Bitmap-Daten ab Adresse 8192/$2000 innerhalb der gewählten VIC-Bank. |

| $D019 | 53273 | 25 | Interrupt Request, Bit (1 = an) Lesen: Bit 7: IRQ durch VIC ausgelöst Bit 6..4: unbenutzt Bit 3: Anforderung durch Lightpen Bit 2: Anforderung durch Sprite-Sprite-Kollision (Reg. $D01E) Bit 1: Anforderung durch Sprite-Hintergrund-Kollision (Reg. $D01F) Bit 0: Anforderung durch Rasterstrahl (Reg. $D012) Schreiben: 1 in jeweiliges Bit schreiben = zugehöriges Interrupt-Flag löschen |

| $D01A | 53274 | 26 | Interrupt Request: Maske, Bit (1 = an) Ist das entsprechende Bit hier und in $D019 gesetzt, wird ein IRQ ausgelöst und Bit 7 in $D019 gesetzt. Bit 7..4: unbenutzt Bit 3: IRQ wird durch Lightpen ausgelöst Bit 2: IRQ wird durch S-S-Kollision ausgelöst Bit 1: IRQ wird durch S-H-Kollision ausgelöst Bit 0: IRQ wird durch Rasterstrahl ausgelöst. |

| $D01B | 53275 | 27 | Priorität Sprite-Hintergrund |

| $D01C | 53276 | 28 | Sprite-Darstellungsmodus, Bit = 1: Sprite n ist Multicolor, sonst einfärbig und hochauflösend (Bitmaske: 0..255) |

| $D01D | 53277 | 29 | Sprite-Schalter, Bit = 1: Sprite n doppelt breit (Bitmaske: 0..255) |

| $D01E | 53278 | 30 | Sprite-Info: Bits = 1: Sprites miteinander kollidiert (Bitmaske: 0..255) Wird durch Zugriff gelöscht. |

| $D01F | 53279 | 31 | Sprite-Info: Bits = 1: Sprite n mit Hintergrund kollidiert (Bitmaske: 0..255) Wird durch Zugriff gelöscht. |

| $D020 | 53280 | 32 | Farbe des Bildschirmrands (0..15) |

| $D021 | 53281 | 33 | Bildschirmhintergrundfarbe (0..15) |

| $D022 | 53282 | 34 | Bildschirmhintergrundfarbe 1 im Extended-Color-Modus und Multicolorfarbe 1 im Multicolor-Modus (0..15) |

| $D023 | 53283 | 35 | Bildschirmhintergrundfarbe 2 im Extended-Color-Modus und Multicolorfarbe 2 im Multicolor-Modus (0..15) |

| $D024 | 53284 | 36 | Bildschirmhintergrundfarbe 3 im Extended-Color-Modus (0..15) |

| $D025 | 53285 | 37 | gemeinsame Sprite-Farbe 0 im Sprite-Multicolor-Modus, Bitkombination %01 (0..15) |

| $D026 | 53286 | 38 | gemeinsame Sprite-Farbe 1 im Sprite-Multicolor-Modus, Bitkombination %11 (0..15) |

| $D027 | 53287 | 39 | Farbe Sprite 0, Bitkombination %10 (0..15) |

| $D028 | 53288 | 40 | Farbe Sprite 1, Bitkombination %10 (0..15) |

| $D029 | 53289 | 41 | Farbe Sprite 2, Bitkombination %10 (0..15) |

| $D02A | 53290 | 42 | Farbe Sprite 3, Bitkombination %10 (0..15) |

| $D02B | 53291 | 43 | Farbe Sprite 4, Bitkombination %10 (0..15) |

| $D02C | 53292 | 44 | Farbe Sprite 5, Bitkombination %10 (0..15) |

| $D02D | 53293 | 45 | Farbe Sprite 6, Bitkombination %10 (0..15) |

| $D02E | 53294 | 46 | Farbe Sprite 7, Bitkombination %10 (0..15) |

| $D02F | 53295 | 47 | nur VIC-IIe (C128) Bit 7..3: unbenutzt |

| $D030 | 53296 | 48 | nur VIC-IIe (C128) Bit 7..2: unbenutzt |

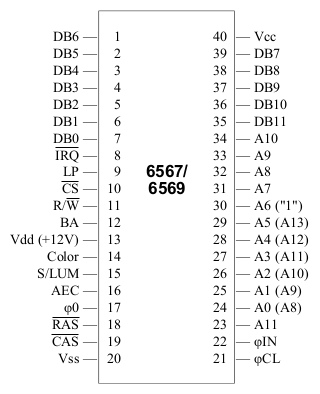

Pinbelegung des MOS 6566/6567/8562 (NTSC) und 6569/8565 (PAL)[Bearbeiten | Quelltext bearbeiten]

| Pin | Beschreibung | |

|---|---|---|

|

DB0 - DB7 | Datenbits 0 - 7 aus RAM bzw. Zeichensatz-ROM |

| DB8 - DB11 | Datenbits 8 - 11 aus Farbram | |

| IRQ | Interrupt-Request, bei LOW wird Interrupt ausgelöst | |

| LP | Lightpen-Eingang | |

| CS | Chip Select - ein Low-Pegel an diesem Eingang bedeutet, dass die Daten am Datenbus gültig sind | |

| R/W | High-Pegel = Register lesen (READ), Low-Pegel = Register schreiben (WRITE) | |

| BA | Bus Available - zeigt an, dass der Bus in der zweiten Takthälfte (phi2 HIGH) für die CPU verfügbar ist | |

| Vdd | Versorgungsspannung +12 V DC (6567/69), oder +5 V DC (8562/65) | |

| Color | Chrominanz, Farbsignal | |

| S/LUM | Sync/Luminanz, S/W-Signal | |

| AEC | Address Enable Control, direkt verbunden mit der CPU. Bei LOW geht die CPU in den Tri-State-Zustand und gibt den Bus frei. | |

| φ0 (phi0) | Systemtakt, generiert aus dem Pixeltakt an Pin φIN mittels Division durch 8 | |

| RAS | Row Address Strobe, zeigt an, dass auf den multiplexten Adressleitungen die Zeilenadresse anliegt | |

| CAS | Column Address Strobe, zeigt an, dass auf den multiplexten Adressleitungen die Spaltenadresse anliegt | |

| Vss | Systemmasse | |

| Vcc | Versorgungsspannung +5 V DC | |

| A0 - A5 | Adressleitungen 0 bis 5, multiplext mit den Adressleitungen A8 - A13 | |

| A6 - A11 | Adressleitungen 6 bis 11 | |

| φIN (phi_IN) | Eingang für Pixeltakt (7,88 MHz für PAL, 8,18 MHz für NTSC) | |

| φCL (phi_CL) | Eingang für den Farbtakt (17,734472 MHz für PAL, 14,31818 MHz für NTSC) |

Kurioserweise besitzt der VIC-II keinen Reset-Pin.

Arbeitsweise[Bearbeiten | Quelltext bearbeiten]

Die Arbeitsweise des VIC-II ist im Dokument "Der MOS 6567/6569 Videocontroller (VIC II) und seine Anwendung im Commodore 64" (1996) von Christian Bauer ausführlich beschrieben. Eine etwas besser lesbare Timing-Übersicht findet sich hier.

Anmerkungen zum Dokument (die englische Variante beinhaltet ein paar der Korrekturen):

- Die Zählung der Zyklen fängt bei 1 an; z.B. VICE fängt bei 0 an zu zählen.

- Im Dokument wird ø0 referenziert, in anderen Quellen ist oft von Phi1 (ø0 low) und Phi2 (ø0 high) die Rede.

- Das Beschreiben von $D011/$D012 kann sofort einen Raster-IRQ auslösen, sofern in der aktuellen Zeile noch kein Raster-IRQ ausgelöst wurde.

- Das vertikale "Expansions-Flipflop" ist unglücklich benannt, tatsächlich gibt sein Zustand an, ob aktuell eine Zeile in den Sprite-Daten vorangesprungen werden soll oder nicht (MCBASE, +3 in zwei Schritten: einmal +2 in Zyklus 15, +1 in Zyklus 16). Der Name "Advance-Flag" oder ähnliches wäre vermutlich passender gewesen. Bei normal großen Sprites ist das Flag immer gesetzt. Bei vertikal doppelt großen Sprites ist es in der ersten Zeile gelöscht, danach wechselt es jede Rasterzeile.

- Sprite-Crunching durch Löschen von Bits in $D017 in Zyklus 15 versetzt MCBASE auf leicht andere Weise als im Dokument angegeben.[11]

- VCBASE und MCBASE werden benutzt, um VC bzw. MC auf Anfangswerte zurückschalten zu können. VCBASE ist der Offset in den Bildschirmspeicher (normaler Textmodus: 0 für Rasterzeilen 51-58, 40 für Rasterzeilen 59-66 und so weiter), MCBASE der Offset innerhalb der Sprite-Daten (0, 3, 6 für normal große Sprites; 0, 0, 3, 3, 6, 6 für vertikal doppelt hohe Sprites).

- VMLI ist kein Pointer, sondern ein 40-Bit-Schieberegister, das die 40 Enable-Bits der VIC-II-internen "40×12 Bit Videomatrix-/Farbzeile" ansteuert. Beim Wechsel vom Idle- in den Display-Zustand wird eine "1" in das Register geschoben und dann nach den C/G-Zugriffen weitergeschoben.

- Bereits eine in Zyklus 15 getriggerte Badline ergibt einen VSP-Versatz um 1. Vermutlich findet die Transition vom Idle in den Display Mode nicht bei der fallenden Flanke von ø0 statt, sondern bei der steigenden Flanke.[12]

- Ein Beispiel zum Timing der Zugriffe (im normalen Textmodus) für die zweite Zeile des Zeichens in der obersten linken Ecke ($0400).

- Welches Zeichen in welcher Farbe dargestellt wird, ergibt sich aus dem C-Zugriff in der Zeile 51 (einer Badline) in der zweiten Hälfte von Zyklus 15.

- Welche Zeichenpixel dargestellt werden, ergibt sich aus dem G-Zugriff in der Zeile 52 in der ersten Hälfte von Zyklus 16.

- Welche Hintergrundfarbe für das Zeichen gilt, ergibt sich aus dem Zustand von $D021 in der Zeile 52 am Ende von Zyklus 17.[13]

Undokumentierte Effekte[Bearbeiten | Quelltext bearbeiten]

- Grafiken im Rahmen durch Rahmensprites lassen sich durch zeitlich abgepasstes Ändern der Scrolling-Register darstellen.

- FLD (Flexible Line Distance)

- VSP (Variable Screen Positioning) bzw. DMA Delay erlaubt das schnelle horizontale Scrollen des Bildschirms über große Distanzen.

- Linecrunch erlaubt das schnelle vertikale Scrollen des Bildschirms über große Distanzen.

- FLI (Flexible Line Interpretation) erlaubt die Nutzung neuer Farben in jeder Zeile.

- FPP (Flexible Picture Positioning)

- Sprite-Stretching und Sprite-Crunching

Eine genauere Beschreibung der Effekte gibt es Codebase64.

In der Zeittafel der C64-Demos wird versucht, die wichtigsten Demos, bei denen Effekte wie diese zum ersten Mal verwendet wurden, in chronologischer Form zusammenzutragen.

Kühlung[Bearbeiten | Quelltext bearbeiten]

In älteren C64 (vor 1986) gehört der VIC zu den heißesten Chips im C64, neben dem SID. In den Boards mit Revision 250407 ist er stets in einem Metallkäfig, der mit einer Kühlzunge mit dem VIC verbunden ist. Bei den Revisionen 250425 und später entfällt dieser häufig - sollte der VIC dennoch unangenehm heiß werden, kann ein Kühlkörper angebracht werden. Besonders heiß werden gern die VICs im Keramik-Gehäuse, und die Oberfläche des Metallkäfigs als zusätzliche Kühlung reicht unter Umständen nicht mehr aus - es können Pixel-Flackerer am Bildschirm entstehen oder gar Abstürze. Bevor hier der VIC für defekt erklärt wird, kann es helfen, die Standard-Fassung auszulöten und eine Präzisionsfassung einzusetzen. Durch dessen bessere Kontakteigenschaften sinkt der Widerstand an den Pins und nebenbei wird noch etwas Wärme nach unten weggeleitet.

Ersatz[Bearbeiten | Quelltext bearbeiten]

Mittlerweile gibt es Ergänzungen und Ersatz des VIC-II, siehe Artikel HF-Modulator.

Weblinks[Bearbeiten | Quelltext bearbeiten]

| Wikipedia: MOS Technology VIC |

| Wikipedia: MOS Technology VIC II |

- Der MOS 6569 (VIC II) im Commodore Computer Online Museum

- Der MOS 6567/6569 Videocontroller (VIC II) und seine Anwendung im Commodore 64 von Christian Bauer. Die englische Variante beinhaltet zusätzlich noch einige Korrekturen.

- Datasheet zum VIC-II (MOS/CSG 6567)

- Mapping the C64 - u.a. Details zur VIC-Programmierung

- Commodore VIC I and VIC II Chips — Bil Herd, Al Charpentier, Stephen Edwards auf YouTube (1:32:21) und Albert Charpentier discusses the VIC chip and the design of the Commodore C64 w/Bil Herd Ben Jordan auf YouTube (1:31:07) - Geschichte und Technik des VIC-I/II direkt von ihrem Entwickler

- Michael Steil: "Rasterstrahl-Hacken: Grafik mit dem Commodore 64" auf YouTube (1:19:46) - einmal (beinahe) alle technischen Details zum VIC-II

- MOS 6569 Die Shots bei Michael Huth

- Thema: VIC2 Die Bilder released (Mikroskopaufnahmen) auf Forum64.de mit ein paar Infos zu Die Shots, Dateien dort leider nicht mehr verfügbar.

Quellen[Bearbeiten | Quelltext bearbeiten]

- ↑ Abschätzung Anzahl Transistoren des VIC-I aus Vergleich des Die-Shots des VIC-II und des VIC-I

- ↑ Abschätzung der Anzahl Transistoren des VIC-II: "VIC-II transistor count"

- ↑ 5µm-Prozess: IEEE Spectrum "Design Case History: the Commodore 64" Seite 49

. MOS beherrschte auch feinere Prozesse, aber nur zu höheren Kosten, siehe "Why did the VIC-II and SID use 6 µm technology in the era of 3 µm and 1.5 µm?"

. MOS beherrschte auch feinere Prozesse, aber nur zu höheren Kosten, siehe "Why did the VIC-II and SID use 6 µm technology in the era of 3 µm and 1.5 µm?"

- ↑ Grobe Überschlagsrechnung zur "Rechenleistung" des VIC-II (die allerdings "fest verdrahtet" ist): Pro_Pixel(Grafik + 8xSprites + Prioritätsberechnung + Kollisionsberechnung) + Pro_Takt(State Machine + Addressberechnung). Grafik ca. 5 Instruktionen (Switch, Shift/Fetch, Mask, Lookup); pro Sprite ca. 5 Instruktionen (Switch, Shift/Fetch, Mask, Lookup); Prioritätsberechnung ca. 6 Instruktionen; Kollisionserkennung ca. 3 Instruktionen; State Machine ca. 10 Instruktionen; Addressberechnung ca. 10 Instruktionen. Macht bei 8 Pixeln pro Takt rund 450 Instruktionen pro Takt/µS, also rund 450 Millionen Instruktionen pro Sekunde. CPUs haben diese Regionen erst Ende der 90er erreicht - sind aber natürlich im Gegensatz zum VIC-II frei programmierbar.

- ↑ Thema: Weiße Punkte bei Raster Interrupt? auf Forum64.de

- ↑ Hintergründe zum Grey Dots Problem

- ↑ Liste von Commodore MOS/CSG ICs

- ↑ Genaugenommen fallen nur 40 Nibbles = 20 Bytes Farbinformationen pro Zeile an, da jedes Nibble aber an einer eigenen Adresse steht, fallen trotzdem 40 RAM-Zugriffe an.

- ↑ Commodore 64 Programmer's Reference, Chapter 3, Screen Memory, p. 102

- ↑ Commodore 64 Programmer's Reference, Chapter 3, Character Memory, p. 103

- ↑ Beim Sprite Crunching kann MCBASE insbesondere auch dekrementiert werden, siehe z.B. den Code in VICE sowie VIC-Addendum.txt dazu.

- ↑ Z.B. x64sc in VICE macht erst in

vicii-cycle.c/vicii_cycle()den G-Zugriff und prüft dann percheck_badline(), ob eine Badline vorliegt, und wechselt ggf. entsprechend in den Display Mode. Kawari implementiert den Effekt, indem am Anfang jedes Zyklus auf das Vorliegen einer Badline geprüft wird [1], jedoch erst am Anfang der zweiten Hälfte erst VC inkrementiert (im Display Mode) und dann ggf. (falls eine Badline vorliegt) vom Idle in den Display Mode gewechselt wird [2]. - ↑ Beachte Anmerkung "es besteht eine Verzögerung von 12 Pixeln" im Abschnitt 3.6.1. des VIC-Artikels.

Hardware-Aufbau des C64 · Hardware-Portalseite

Komponenten des C64: CPU · VIC · SID · CIA · PLA · RAM · ROM · Farb-RAM